芯片制造知识讲解:PIE知识问答

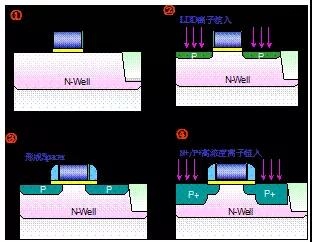

1、LDD是什幺的缩写? 用途为何?

答:LDD: Lightly Doped Drain. LDD是使用较低浓度的源/漏极, 以防止组件产生热载子效应的一项工艺。

2、何谓 Hot carrier effect (热载流子效应)?

答:在线寛小于0.5um以下时, 因为源/漏极间的高浓度所产生的高电场,导致载流子在移动时被加速产生热载子效应, 此热载子效应会对gate oxide造成破坏, 造成组件损伤。

3、何谓Spacer? Spacer蚀刻时要注意哪些地方?

答:在栅极(Poly)的两旁用dielectric(介电质)形成的侧壁,主要由Ox/SiN/Ox组成。蚀刻spacer 时要注意其CD大小,profile(剖面轮廓),及remain oxide(残留氧化层的厚度)。

4、Spacer的主要功能?

答:①使高浓度的源/漏极与栅极间产生一段LDD区域; ②作为Contact Etch时栅极的保护层。

5、为何在离子注入后, 需要热处理( Thermal Anneal)的工艺?

答:①为恢复经离子注入后造成的芯片表面损伤; ②使注入离子扩散至适当的深度; ③使注入离子移动到适当的晶格位置。

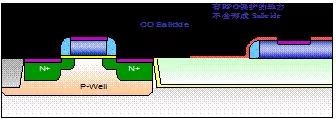

6、SAB是什幺的缩写? 目的为何?答:SAB:Salicide block, 用于保护硅片表面,在RPO (Resist Protect Oxide) 的保护下硅片不与其它Ti, Co形成硅化物(salicide)。

7、简单说明SAB工艺的流层中要注意哪些?

答:①SAB 光刻后(photo),刻蚀后(etch)的图案(特别是小块区域)。要确定有完整的包覆(block)住必需被包覆(block)的地方。 ②remain oxide (残留氧化层的厚度)。

8、何谓硅化物( salicide)?

答:Si 与 Ti 或 Co 形成 TiSix 或 CoSix, 一般来说是用来降低接触电阻值(Rs, Rc)。

9、硅化物(salicide)的形成步骤主要可分为哪些?

答:①Co(或Ti)+TiN的沉积;②第一次RTA(快速热处理)来形成Salicide。③将未反应的Co(Ti)以化学酸去除。④第二次RTA (用来形成Ti的晶相转化, 降低其阻值)。

10、MOS器件的主要特性是什幺?答:它主要是通过栅极电压(Vg)来控制源,漏极(S/D)之间电流,实现其开关特性。

11、我们一般用哪些参数来评价device的特性?

答:主要有Idsat、Ioff、Vt、Vbk(breakdown)、Rs、Rc;一般要求Idsat、Vbk (breakdown)值尽量大, Ioff、Rc尽量小,Vt、Rs尽量接近设计值.

12、什幺是Idsat?Idsat 代表什幺意义?

答:饱和电流。也就是在栅压(Vg)一定时,源/漏(Source/Drain)之间流动的最大电流。

13、在工艺制作过程中哪些工艺可以影响到Idsat?

答:Poly CD(多晶硅尺寸)、Gate oxide Thk(栅氧化层厚度)、AA(有源区)宽度、Vt imp.条件、LDD imp.条件、N+/P+ imp. 条件。

14、什幺是Vt? Vt 代表什幺意义?

答:阈值电压(Threshold Voltage),就是产生强反转所需的最小电压。当栅极电压Vg<Vt时, MOS处于关的状态,而Vg〉=Vt时,源/漏之间便产生导电沟道,MOS处于开的状态。

15、在工艺制作过程中哪些工艺可以影响到Vt?

答:Poly CD、Gate oxide Thk. (栅氧化层厚度)、AA(有源区)宽度及Vt imp.条件。

16、什幺是Ioff? Ioff小有什幺好处

答:关态电流,Vg=0时的源、漏级之间的电流,一般要求此电流值越小越好。Ioff越小, 表示栅极的控制能力愈好, 可以避免不必要的漏电流(省电)。

17、什幺是 device breakdown voltage?

答:指崩溃电压(击穿电压),在 Vg=Vs=0时,Vd所能承受的最大电压,当Vd大于此电压时,源、漏之间形成导电沟道而不受栅压的影响。在器件越做越小的情况下,这种情形会将会越来越严重。

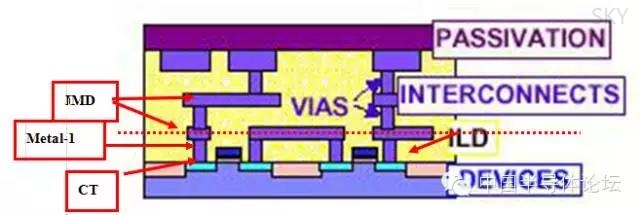

18、何谓ILD? IMD? 其目的为何?

答: ILD :Inter Layer Dielectric, 是用来做device 与 第一层metal 的隔离(isolation),而IMD:Inter Metal Dielectric,是用来做metal 与 metal 的隔离(isolation).要注意ILD及IMD在CMP后的厚度控制。

19、一般介电层ILD的形成由那些层次组成?

答:① SiON层沉积(用来避免上层B,P渗入器件);② BPSG(掺有硼、磷的硅玻璃)层沉积;③ PETEOS(等离子体增强正硅酸乙脂)层沉积;最后再经ILD Oxide CMP(SiO2的化学机械研磨)来做平坦化。

20、一般介电层IMD的形成由那些层次组成?答:① SRO层沉积(用来避免上层的氟离子往下渗入器件);② HDP-FSG(掺有氟离子的硅玻璃)层沉积;

③ PE-FSG(等离子体增强,掺有氟离子的硅玻璃)层沉积;

使用FSG的目的是用来降低dielectric k值, 减低金属层间的寄生电容。最后再经IMD Oxide CMP(SiO2的化学机械研磨)来做平坦化。

21、简单说明Contact(CT)的形成步骤有那些?答:Contact是指器件与金属线连接部分,分布在poly、AA上。

① Contact的Photo(光刻);

② Contact的Etch及光刻胶去除(ash & PR strip);

③ Glue layer(粘合层)的沉积;

④ CVD W(钨)的沉积

⑤ W-CMP 。

22、Glue layer(粘合层)的沉积所处的位置、成分、薄膜沉积方法是什幺?答:因为W较难附着在Salicide上,所以必须先沉积只Glue layer再沉积WGlue layer是为了增强粘合性而加入的一层。主要在salicide与W(CT)、W(VIA)与metal之间, 其成分为Ti和TiN, 分别采用PVD 和CVD方式制作。

23、为何各金属层之间的连接大多都是采用CVD的W-plug(钨插塞)?

答:① 因为W有较低的电阻;② W有较佳的step coverage(阶梯覆盖能力)。

24、一般金属层(metal layer)的形成工艺是采用哪种方式?大致可分为那些步骤?答:① PVD (物理气相淀积) Metal film 沉积;② 光刻(Photo)及图形的形成;③ Metal film etch 及plasma(等离子体)清洗(此步驺为连序工艺,在同一个机台内完成,其目的在避免金属腐蚀);④ Solvent光刻胶去除。

25、Top metal和inter metal的厚度,线宽有何不同?答:Top metal通常要比inter metal厚得多,0.18um工艺中inter metal为4KA,而top metal要8KA.主要是因为top metal直接与外部电路相接,所承受负载较大。一般top metal 的线宽也比 inter metal宽些。

26、在量测Contact /Via(是指metal与metal之间的连接)的接触窗开的好不好时, 我们是利用什幺电性参数来得知的?

答:通过Contact 或Via的 Rc值,Rc值越高,代表接触窗的电阻越大, 一般来说我们希望Rc是越小越好的。

27、什幺是Rc? Rc代表什幺意义?

答:接触窗电阻,具体指金属和半导体(contact)或金属和金属(via),在相接触时在节处所形成的电阻,一般要求此电阻越小越好。

28、影响Contact (CT) Rc的主要原因可能有哪些?

答:①ILD CMP 的厚度是否异常;②CT 的CD大小;③CT 的刻蚀过程是否正常;④接触底材的质量或浓度(Salicide,non-salicide);⑤CT的glue layer(粘合层)形成;⑥CT的W-plug。

29、在量测Poly/metal导线的特性时, 是利用什幺电性参数得知?答:可由电性量测所得的spacing & Rs 值来表现导线是否异常。

30、什幺是spacing?如何量测?

答:在电性测量中,给一条线(poly or metal)加一定电压,测量与此线相邻但不相交的另外一线的电流,此电流越小越好。当电流偏大时代表导线间可能发生短路的现象。

31、什幺是 Rs?

答:片电阻(单位面积、单位长度的电阻),用来量测导线的导电情况如何。一般可以量测的为 AA(N+,P+), poly & metal.

32、影响Rs有那些工艺?

答:① 导线line(AA, poly & metal)的尺寸大小。(CD=critical dimension)

② 导线line(poly & metal)的厚度。

③ 导线line (AA, poly & metal) 的本身电导性。(在AA, poly line 时可能为注入离子的剂量有关)

33、一般护层的结构是由哪三层组成?

答:① HDP Oxide(高浓度等离子体二氧化硅);② SRO Oxide(Silicon rich oxygen富氧二氧化硅);

③ SiN Oxide

34、护层的功能是什幺?

答:使用oxide或SiN层, 用来保护下层的线路,以避免与外界的水汽、空气相接触而造成电路损害。

35、Alloy 的目的为何?

答:① Release 各层间的stress(应力),形成良好的层与层之间的接触面;② 降低层与层接触面之间的电阻。

36、工艺流程结束后有一步骤为WAT,其目的为何?答:WAT(wafer acceptance test), 是在工艺流程结束后对芯片做的电性测量,用来检验各段工艺流程是否符合标准。(前段所讲电学参数Idsat, Ioff, Vt, Vbk(breakdown), Rs, Rc就是在此步骤完成)

37、WAT电性测试的主要项目有那些?

答:① 器件特性测试;② Contact resistant (Rc);③ Sheet resistant (Rs);④ Break down test;⑤ 电容测试;⑥ Isolation (spacing test)。

38、什么是WAT Watch系统? 它有什么功能?答:Watch系统提供PIE工程师一个工具, 来针对不同WAT测试项目,设置不同的栏住产品及发出Warning警告标准, 能使PIE工程师早期发现工艺上的问题。

39、什么是PCM SPEC?

答:PCM (Process control monitor) SPEC广义而言是指芯片制造过程中所有工艺量测项目的规格,狭义而言则是指WAT测试参数的规格。

40、当WAT量测到异常是要如何处理?

答:① 查看WAT机台是否异常,若有则重测之;② 利用手动机台Double confirm;③ 检查产品是在工艺流程制作上是否有异常记录;④ 切片检查

41、什么是EN? EN有何功能或用途?答:由CE发出,详记关于某一产品的相关信息(包括Technology ID, Reticle and some split condition ETC….) 或是客户要求的事项 (包括HOLD, Split, Bank, Run to complete, Package….), 根据EN提供信息我们才可以建立Process flow及处理此产品的相关动作。

42、PIE工程师每天来公司需要Check哪些项目(开门五件事)?答:① Check MES系统, 察看自己Lot情况;② 处理in line hold lot.(defect, process, WAT);③ 分析汇总相关产品in line数据.(raw data & SPC);④ 分析汇总相关产品CP test结果;⑤ 参加晨会, 汇报相关产品信息